- Circuit: 8-bit unsigned adders

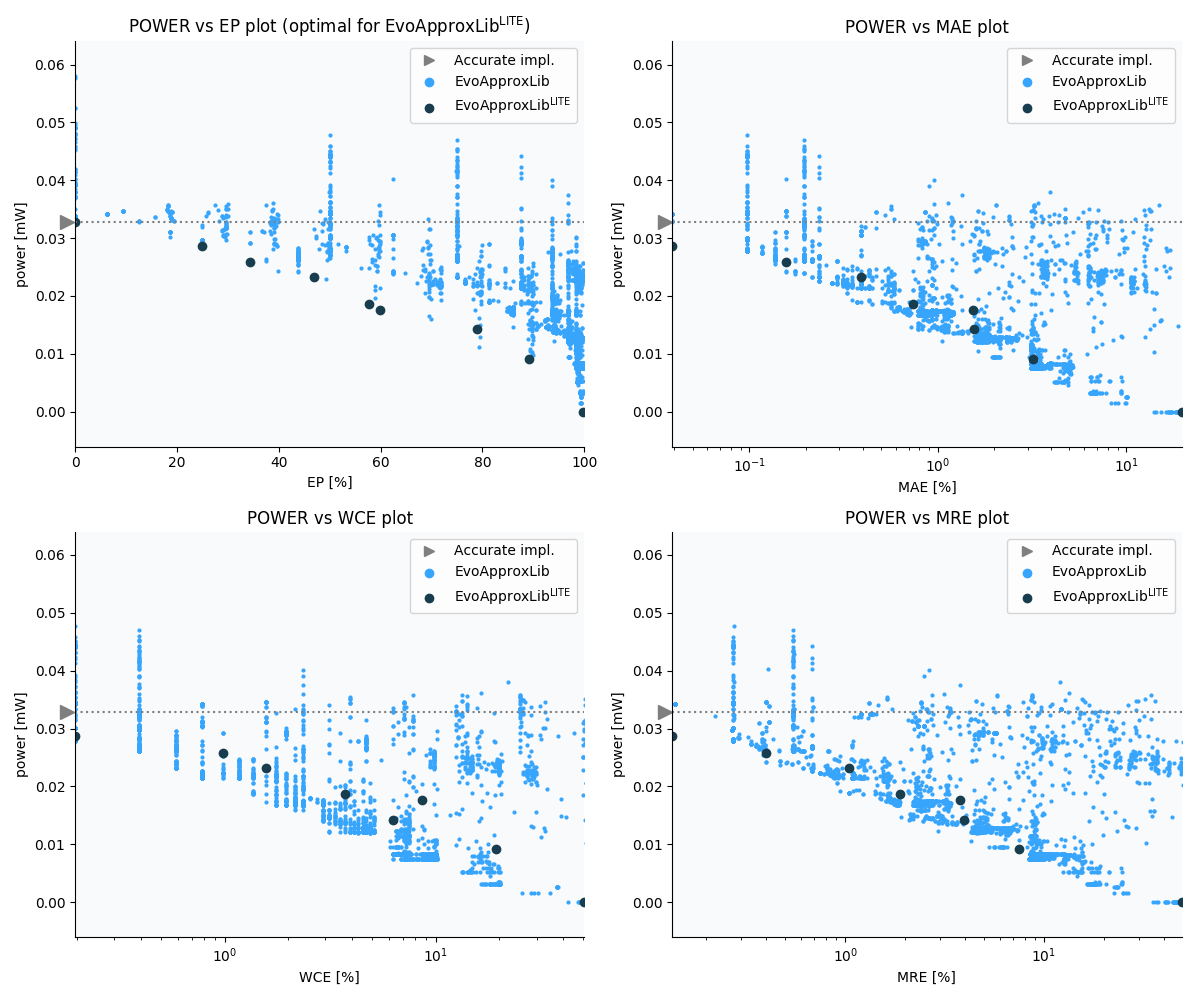

- Selection criteria: pareto optimal sub-set wrt. pwr and ep parameters

| Circuit name | MAE% | WCE% | EP% | MRE% | MSE | Download |

|---|---|---|---|---|---|---|

| add8u_0FP | 0.00 | 0.00 | 0.00 | 0.00 | 0 | [Verilog] [C] |

| add8u_5R3 | 0.039 | 0.20 | 25.00 | 0.14 | 0.2 | [Verilog] [VerilogPDK45] [C] |

| add8u_5NQ | 0.16 | 0.98 | 34.38 | 0.40 | 2.5 | [Verilog] [VerilogPDK45] [C] |

| add8u_8MK | 0.39 | 1.56 | 46.88 | 1.04 | 10 | [Verilog] [C] |

| add8u_8FF | 0.74 | 3.71 | 57.81 | 1.89 | 46 | [Verilog] [C] |

| add8u_8FD | 1.54 | 8.59 | 59.96 | 3.76 | 190 | [Verilog] [C] |

| add8u_8KJ | 1.56 | 6.25 | 78.91 | 3.97 | 124 | [Verilog] [C] |

| add8u_8BB | 3.20 | 19.34 | 89.23 | 7.47 | 745 | [Verilog] [C] |

| add8u_88L | 19.67 | 50.39 | 99.77 | 49.16 | 14074 | [Verilog] [C] |

- V. Mrazek, Z. Vasicek and R. Hrbacek, "Role of circuit representation in evolutionary design of energy-efficient approximate circuits" in IET Computers & Digital Techniques, vol. 12, no. 4, pp. 139-149, 7 2018. doi: 10.1049/iet-cdt.2017.0188

- V. Mrazek, R. Hrbacek, Z. Vasicek and L. Sekanina, "EvoApprox8b: Library of approximate adders and multipliers for circuit design and benchmarking of approximation methods". Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017, Lausanne, 2017, pp. 258-261. doi: 10.23919/DATE.2017.7926993

- V. Mrazek, L. Sekanina, Z. Vasicek "Libraries of Approximate Circuits: Automated Design and Application in CNN Accelerators" IEEE Journal on Emerging and Selected Topics in Circuits and Systems, Vol 10, No 4, 2020