GaN Transistors for Efficient Power Conversion. (2014). https://doi.org/10.1002/9781118844779

-

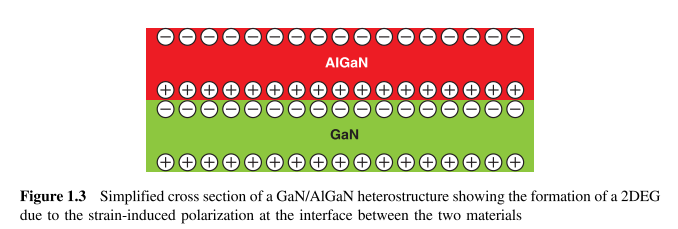

Crystal structure also gives GaN piezoelectric properties that lead to its ability to achieve very high conductivity compared with other semiconductor materials. Piezoelectricity in GaN is predominantly caused by the displacement of charged elements in the crystal lattice. If the lattice is subjected to strain, the deformation will cause a miniscule shift in the atoms in the lattice that generate an electric field – the higher the strain, the greater the electric field. By growing a thin layer of AlGaN on top of a GaN crystal, a strain is created at the interface that induces a compensating two- dimensional electron gas (2DEG).

-

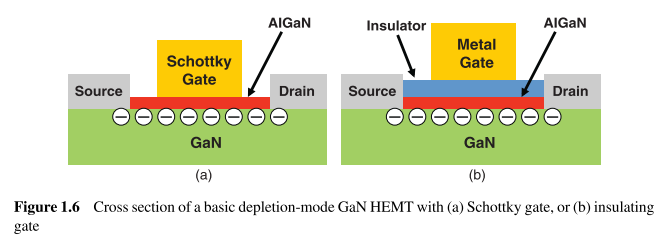

When a negative voltage relative to both drain and source electrodes is applied to the gate, the electrons in the 2DEG are depleted out of the device. This type of transistor is called a depletion-mode, or d-mode, HEMT. Normally ON

-

A D-Mode GaN structure can be implemented with Schottky Gate or with a Metal Gate with insulator like MOSFETs.

-

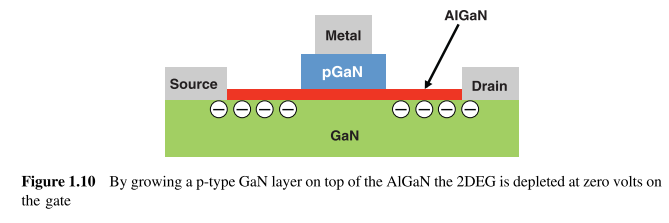

An enhancement-mode (e-mode) device, on the other hand, would not suffer this limitation. With zero bias on the gate, an e-mode device is OFF. There are four popular structures that have been used to create enhancement-mode devices: recessed gate, implanted gate, pGaN gate, and cascode hybrid.

-

p-GaN Gate: The positive charges in this pGaN layer have a built-in voltage that is larger than the voltage generated by the piezoelectric effect, thus depleting the electrons in the 2DEG and creating an enhancement-mode structure

-

Cascode: A Si MOSFET is placed in series with a D-mode HEMT device

-

When the GaN layer exceeds ECrit (GaN), a different mechanism causes device failure. When breakdown occurs in the GaN or Al GaN regions, the electrons generated can destroy the 2DEG, causing the device on-resistance to increase greatly: ** Breakdown causes open circuit**

-

Because the strain in the AlGaN barrier is relatively constant with temperature, as are the voltages generated by the internal metallurgy, the threshold voltage in a GaN HEMT is relatively constant with temperature

-

The reason for the drop in capacitance as VDS increases is that the free electrons in the GaN are depleted. For example, the initial step down in COSS is caused by the depletion of the 2DEG near the surface. Higher VDS values extend the depletion region laterally from the field plate edge to the drain, further depleting the 2DEG and eliminating its capacitive component

-

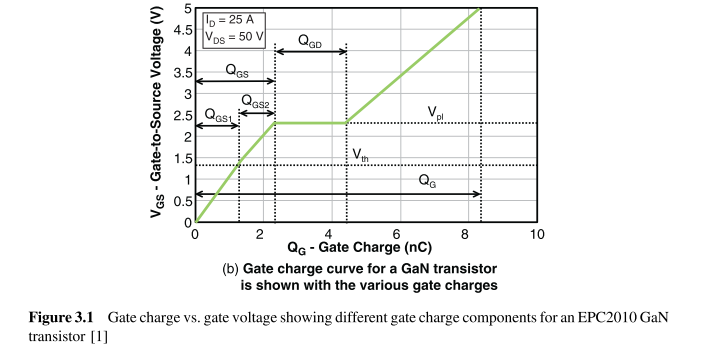

The QGD and QGS are also specified separately because they impact the voltage- and current- switching transition speeds, respectively. Also, the ratio of these two values, QGD/QGS, called the Miller ratio, is often an important metric to determine the point at which a device might turn on due to a voltage transient applied across the drain and source.

Switching Transient Analysis for Normally-Off GaN Transistors with p-GaN Gate in a Phase-Leg Circuit. IEEE Transactions on Power Electronics, PP(c), 1–1. https://doi.org/10.1109/TPEL.2018.2852142

-

Owing to the p-GaN layer inserted between the gate electrode and the AlGaN barrier, a p-GaN/gate-metal Schottky junction (J1) and a p-GaN/AlGaN heterojunction (J2) would be formed. when a high drain-to-gate stress (Vdg-stress) is applied, where J1 is forward biased while J2 is reversely biased. As a result, the holes in p-GaN layer are more prone to enter into the gate electrode. Once the drain voltage stress is removed, because of J1’s low reverse leakage current, the removed positive charges in p-GaN could not be quickly recovered [23], leading to a positive shift in Vth.

-

During the switching transient process, the depletion region of Schottky junction J1 would be widened because of the removed holes in p-GaN layer [23]. Therefore, both the Schottky junction J1 and heterojunction J2 would be reversely biased. Taking J1 as an example, during a switching period, the charging/discharging current of intrinsic capacitance C1 would be 1.5

1.9x104 times higher than its leakage current (0.4A0.6A vs. 21.1µA~39.3µA). Consequently, the diode would not be taken into consideration in the circuit-level analysis, on account of the dominant role played by capacitance’s displacement current.

Jones, E. A., Wang, F. F., & Costinett, D. (2016). Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE Journal of Emerging and Selected Topics in Power Electronics, 4(3), 707–719. https://doi.org/10.1109/JESTPE.2016.2582685

-

At the interface between these two layers, a layer of high-mobility electrons called “two-dimensional electron gas” (2DEG) forms as a result of the crystal polarity, and is also augmented by piezoelectric crystal strain due to the lattice mismatch between AlGaN and GaN.

-

When this voltage exceeds the threshold voltage Vgd,th, which is typically approximately the same as the specified Vgs,th, the e-mode device channel will turn on and allow reverse current to flow.

-

The voltage drop in the SCRC mode will then be, eqn, where Rsd,rev is the effective channel resistance during SCRC. Rsd,rev is typically higher than Rds,on and varies with Tj , Vgs, and Id.

-

Current collapse has been a widely reported phenomenon for lateral GaN devices, causing a temporary increase in ON-resistance that is proportional to blocking voltage. The first is the trapping of surface charges near the drain edge of the gate terminal when the device is in its OFF-state. During the following ON-state, these trapped charges act as a virtual gate, weakening the 2DEG until they are released. The second mechanism is the injection of hot electrons into even deeper traps within the device, particularly in traps caused by carbon doping in the buffer layer. These trapped charges weaken the 2DEG and increase Rds,on,and may also cause long-term degradation to the device.

-

Source and gate field plates help to redistribute the gate–drain electric field away from the gate edge.

-

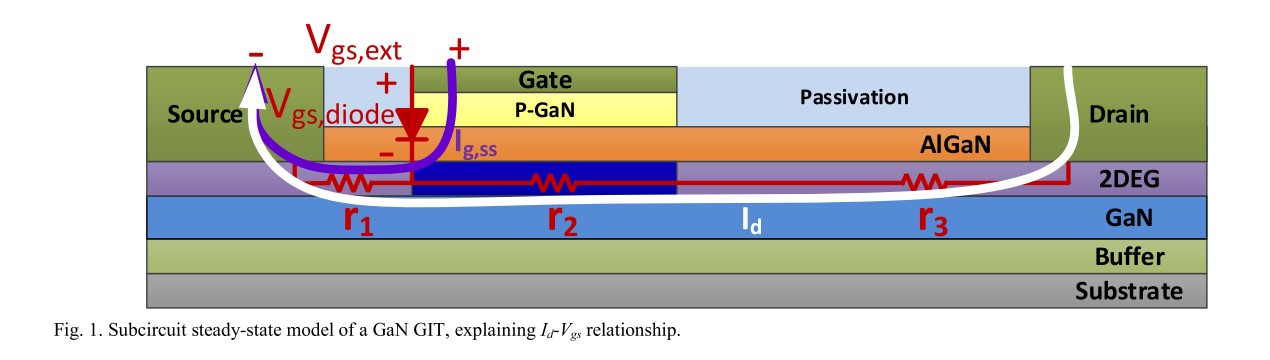

Steady-state gate current is expected during normal operation for e-mode HFETs with p-doped gate caps.

-

The threshold voltage of most GaN devices is relatively stable over temperature.

M. Landel, S. Lefebvre, D. Labrousse, C. Gautier, F. Zaki, and Z. Khatir, “Dispersion of electrical characteristics and short-circuit robustness of 600V E-mode GaN transistors,” PCIM Eur. 2017 - Int. Exhib. Conf. Power Electron. Intell. Motion, Renew. Energy Energy Manag., no. May, pp. 16–18, 2017.

-

We begin with the gate lag phenomenon, which concerns rather traps behaviour under the gate. It can explain the dispersion of the threshold voltage.

-

There is a remarkable dispersion qualitatively and quantitatively. This is noticed on the time constants that reflects dispersion in the traps activation energies, and also on their amplitude, which reflects dispersion in their density. On the other hand, we notice a qualitative increase and/or decrease in each curve, which may reveals the existence of traps in AlGaN and GaN layer simultaneously. These traps may have contradictory effects on the 2DEG concentration whether they are located in GaN or AlGaN layer.

-

We performed the same study on the drain lag. To this end, we applied a drain voltage of 600 V in the OFF-State for 1 s and 1 V in the ON-State in order to activate the maximum of trap energy levels. In the following we present the transient currents that illustrate the dispersion between the components at the level of the drain traps.

-

We note a different behavior compared to the Gate Lag. The current collapses at the beginning, due to the effect of the high voltage applied during the OFF-state, which depletes totally the channel.

-

Also note that most devices may take a very long time to return to their initial state, even on this time scale, we find that there are some devices that have not yet stabilized.

R. Hou, J. Lu, and D. Chen, “An Ultrafast Discrete Short-Circuit Protection Circuit for GaN HEMTs,” pp. 1920–1925, 2018.,

-

One of the factors that yield the saturation current reduction is due to the temperature-dependent transconductance in the 2DEG channel of GaN HEMT. Clearly, with higher junction temperature, the saturation current gets lower.

-

The second factor that contributes to the saturation current reduction can be on the gate. It has been proven that the fast increase of the temperature has an effect on the gate current [9]. With a higher temperature, the gate current becomes higher. Therefore, it introduces a larger voltage drop on the gate. This can be another reason cause the saturation current reduction.

G. Mishemts et al., “Short-Circuit Study in Medium-Voltage GaN,” vol. 64, no. 11, pp. 9012–9022, 2017. 10.1109/TIE.2017.2719599

- The main problems of the available GaN cascodes are related to its packaging, which, in combination with control and power loop inductances, is responsible for the observed gate ringing. Under a SC event in a real application, this ringing could lead to the device destruction or converter failure, even after withstanding such an electrical stress. In this regard, gate bipolar control and reducing loop inductances could assist to improve cascodes SC ruggedness. Moreover, the low thermal self-regulation on their gate control makes them less rugged than EHEMTs to SC events. However, GaN cascodes present an inherent pn- junction structure at the Si MOSFET, which can be used as a free-wheeling diode with a significantly lower forward voltage (integral diode +DHEMT) drop than EHEMTs. This is of interest for synchronous rectification, e.g., power inverters for motor driving. As another benefit, GaN cascodes can be controlled using traditional VG values.

GaN Transistors for Efficient Power Conversion. (2014). https://doi.org/10.1002/9781118844779

-

The voltage overshoot damping rate is dependent on the skin and proximity effect losses at the ringing frequency. To approximate this, a parallel damping resistance of 1Ω is placed across each of the parasitic inductance elements.

-

The plateau voltage is where the current crosses Vgs at specific Vds values.

GaN Transistors for Efficient Power Conversion. (2014). https://doi.org/10.1002/9781118844779

-

It is often very convenient to look at the amount of charge necessary to change the voltage across various terminals in the GaN HEMT.

-

QGS: Charge required to increase gate voltage from zero to the plateau voltage.

QGS1: Charge required to increase gate voltage from zero to the threshold voltage of the device.

QGS2: Charge required to commutate the device current.

QGS = QGS1 + QGS2

QGD: Charge required to commutate the device voltage, at which point the device enters the linear region.

QG: Total gate charge required to drive a device from zero to rated gate voltage, including QGD

-

Self-commutation transitions have zero POSS losses, but only if the load current is sufficient to completely charge COSS to VBUS or discharge to zero, and if the time to complete the self-commutation transition is much longer than the current transition time of the device itself.

-

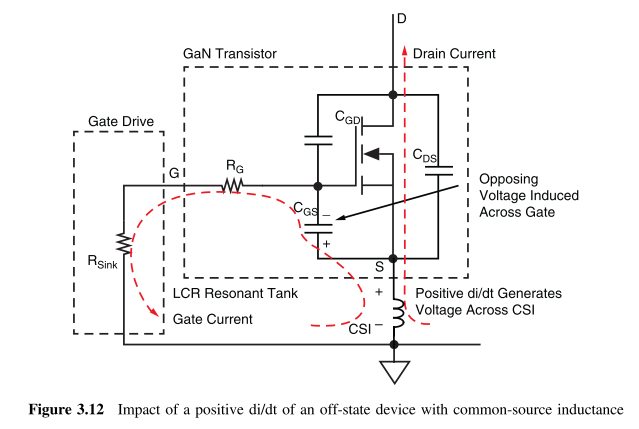

During a current transition event, the voltage generated across the common source inductance will oppose the gate voltage, thereby reducing the gate current used to charge the gate capacitance. This effectively lengthens the current transition period.

-

The power loop inductance has two main negative effects on the switch during turn-off: it slows the transition and it increases the voltage across the drain and source. During device turn- on, the loop inductance reduces the device drain-to-source voltage, which decreases losses. However, the sum of the two negative effects and the positive effect has a net negative result, which means that the loop inductance will increase losses in the circuit

Jones, E. A., Wang, F. F., & Costinett, D. (2016). Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE Journal of Emerging and Selected Topics in Power Electronics, 4(3), 707–719. https://doi.org/10.1109/JESTPE.2016.2582685

-

The switching performance of the cascode device relies heavily on the parasitic inductances in the package, especially between the two dies, and also on how well the junction capacitances of the two are matched. If the inductances are too high, or the capacitances are not matched well, the switching losses can increase significantly.

-

In hard-switched converters, the two significant sources of switching energy losses are the energy related to stored charge in the output capacitors (Coss loss) and the loss from conduction of the load current through a saturated device channel (overlap loss).

Jones, E. A., Wang, F. F., & Costinett, D. (2016). Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE Journal of Emerging and Selected Topics in Power Electronics, 4(3), 707–719. https://doi.org/10.1109/JESTPE.2016.2582685

- Some devices provide a Kelvin source connection, which is a separate connection to the source metallization that is only used by the gate loop, decoupling it more effectively from power loop transient effects [65]–[68].

GaN Transistors for Efficient Power Conversion. (2014). https://doi.org/10.1002/9781118844779

-

To critically damp this loop, the overall gate loop resistance RG(eq) (RG(eq) =RG +RSource ) must be larger than the value given in Equation 3.1. This is achieved by minimizing the gate loop inductance (LG) and adjusting the series gate resistance to limit overshoot.

$R_g(eq) >= sqrt{4*L_g/C_gs}$ -

Since the turn-on and turn-off damping requirements are different, the minimum gate loop resistance values will also differ. These differences are best addressed by separating the pull-up and pull-down gate driver resistances at the driver output (creating two separate driver outputs), thus allowing the use of two separate gate resistors to independently adjust the turn-on and turn- off gate loop damping.

-

The concern is that, unless addressed, the charging current through the CGD capacitor will flow through and charge CGS beyond Vth and turn the device on. This event, sometimes called Miller turn-on, can be very dissipative

-

To determine the dv/dt susceptibility of a power device, a Miller charge ratio (QGD/QGS1), as function of drain-to-source voltage, needs to be evaluated. A Miller ratio of less than one will guarantee dv/dt immunity.

-

A rising current through an off-state device, as shown in Figure 3.12, will induce a step voltage across the common-source inductance (CSI). The CSI is the inductance on the source side of a device that is common to both the power loop (drain-to-source current) and the gate drive loop (gate-to-source current).

-

A better solution is to limit the size of the CSI through improved packaging and device layout. This is accomplished by separating the gate and power loops to as close to the GaN device as possible, and minimizing the internal source inductance of the GaN device, which will remain common to both loops.

-

There is a tradeoff between too much filtering causing significant delay and pulse width distortion due to variation in the gate driver input thresholds, or not enough filtering maintaining susceptibility to logic glitches. The second alternative solution is to use a level-shifter or isolator between the controller and the gate driver. This approach effectively treats the low-side gate driver the same way as the floating high-side driver. Although a level-shifter increases complexity and component count, it does have the added advantage of improving the gate driver propagation delay matching between the high side and low side.

Jones, E. A., Wang, F. F., & Costinett, D. (2016). Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE Journal of Emerging and Selected Topics in Power Electronics, 4(3), 707–719. https://doi.org/10.1109/JESTPE.2016.2582685

- It is generally concluded that these RF-based digital isolators tolerate higher dv/dt than alterna- tives.

Zhao, Q., & Stojcic, G. (2007). Characterization of Cdv/dt induced power loss in synchronous buck DC-DC converters. IEEE Transactions on Power Electronics, 22(4), 1508–1513. https://doi.org/10.1109/TPEL.2007.900527

-

One of the issues frequently discussed but not fully understood or characterized is so-called induced switching loss of MOS-FETs used as synchronous rectifier

-

The increased voltage across the sync FET induces a current to charge the gate through the gate-to-drain capacitor, . The induced voltage can possibly invert (turn-on) the sync FET channel for a short time period. The overlapping of the voltage and the current generates additional switching loss.

-

The idea is to modify the gate drive circuit so that an adjustable negative gate-source offset voltage can be generated. The purpose of the negative offset voltage is to shift the induced gate voltage below the gate threshold voltage. By applying a sufficient negative offset, the induced turn on loss can be completely eliminated.

-

The benefit of CdV/dt induced turn on is the reduced peak voltage stress of the sync FET. The optimized design is to minimize the induced loss and total losses while the maximum voltage stress of the sync FET is less than the specification.

GaN Transistors for Efficient Power Conversion. (2014). https://doi.org/10.1002/9781118844779

-

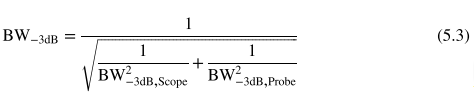

To yield an accurate representation of the waveform rise time, a rule of thumb is that a bandwidth between three and five times that of Equation 5.1 is required

-

However, the oscilloscope alone cannot measure the switching waveforms. A voltage probe, with its own associated bandwidth limitations, is also required. For such a cascade system, the effective rise time is given by the root-mean-square (RMS) of separate component rise times. This can be expressed in terms of component bandwidths as in Equation 5.3 [13]:

-

Due to their size and shape, coaxial shunts add a larger amount of inductance to the overall circuit, and any significant increase in power loop inductance will adversely affect switching operation.

Xie, R., Yang, X., Xu, G., Wei, J., Wang, Y., Wang, H., … Chen, K. J. (2018). Switching Transient Analysis for Normally-Off GaN Transistors with p-GaN Gate in a Phase-Leg Circuit. IEEE Transactions on Power Electronics, PP(c), 1–1. https://doi.org/10.1109/TPEL.2018.2852142

- The C-V measurement is conducted as follows. Under a given gate bias condition, a high-frequency

(e.g. 1MHz) AC voltage signal would be applied to the capacitor under test. By measuring the output

current, the impedance (which includes conductance and capacitance) value could be calculated.

However, some terminal capacitances, such as gate-to-drain capacitance (Cgd), could not be directly

measured without additional setups. As illustrated in Fig. 6(a), by connecting device’s S terminal

to AC guard, the AC disturbance signal would be cut off. As a result, the Cgd-Vdg curve could be

acquired.

Nibir, S. J., Fregosi, D., & Parkhideh, B. (2018). Investigations on Circuits and Layout for Non- Intrusive Switch Current Measurements in High Frequency Converters using Parallel GaN HEMTs, 2743–2748. https://doi.org/10.1109/APEC.2018.8341405

-

Recently Magnetoresistor (MR) based current sensors are gaining popularity for high frequency current sensing in power electronic applications due to their inherent capability of responding to high frequency transients and lower temperature drift [15]-[19].

-

The sensors are placed in such a way that the magnetic field generated by the current flowing through the GaN transistors (as shown in Yellow lines in Fig. 4) crosses the sensors through their sensing axis.

-

Theoretically, they also should not have any impact on the switch current measurement by the AMR sensor.

Jones, E. A., Williford, P., & Wang, F. (2017). A fast overcurrent protection scheme for GaN GITs. 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications, WiPDA 2017, 2017–December, 277–284. https://doi.org/10.1109/WiPDA.2017.8170560

-

The desaturation detection circuit’s sensing diode requires significant settling time after the drain voltage falls in turn-on transients. This diode also adds capacitive loading in parallel with the output capacitance, which increases switching loss.

-

The internal gate voltage acts as a diode, due to the junction created by the p-doped GaN layer implanted beneath the gate metallization. As with a discrete diode, there is a measurable relationship between its voltage and current.

The main logic is that

i) The gate of the GIT device sinks a current under steady state operation

ii) Therefore, Vgs,diode is constant for steady-State

iii) There is a relation between Id and Vgs,ext which says the current can be followed through Vgs,ext

-

Vgs,sense must be filtered for immunity to turn-on transient spikes and noise

-

One of the reasons that strong noise immunity and fast response are expected from this protection circuit is that it uses the same references and supply voltages as the gate driver IC, avoiding the need for any isolation between the sensed gate voltage and the comparator circuit.

Awwad, A. E., & Dieckerhoff, S. (n.d.). Short-Circuit Evaluation and Overcurrent Protection for SiC Power MOSFETs Keywords Short-Circuit Behavior of SiC Power MOSFETs.

-

The short-circuit tests are conducted with the circuit given below.

-

The stray inductance and thermal effects need to be considered to describe the short circuit current characteristics

-

It is obvious that a change of the external gate resistance (in the example from Rg=12Ω to 90Ω) has only a marginal impact on the peak short circuit current. The gate resistance determines the time constant RgCeq at which the gate is charged, and hence influences the di/dt during the charging process.

-

The parasitic method shows a faster detection time than the desaturation method. The larger delay in the desaturation method is mainly due to the junction capacitance of the DDESAT and its reverse recovery characteristics [10-12].

-

The desaturation method shows a higher fault response time compared to the parasitics technique. Using the parasitics method, the maximum fault current is reduced by around 20%.

G. Mishemts et al., “Short-Circuit Study in Medium-Voltage GaN,” vol. 64, no. 11, pp. 9012–9022, 2017. 10.1109/TIE.2017.2719599

-

EHEMTs have the main drawback of overheating under operating conditions, which decrease the µ(T) and degrades RDS(on) . Fortunately, this thermal behavior is beneficial for their SC ruggedness, as a self-regulation process on ID takes place.

-

The figure given below SC ruggedness of different type of transistors.

B. Huang, Y. Li, T. Q. Zheng, and Y. Zhang, “Design of overcurrent protection circuit for GaN HEMT,” in 2014 IEEE Energy Conversion Congress and Exposition, ECCE 2014, 2014, pp. 2844–2848.

-

From the table we can know, the gate threshold voltage of the device is just 1.4V, which is far below the silicon power MOSFET’s, which leads to an easier conduction false. Its parasitic capacitors, which include input capacitor (Ciss) and output capacitor (Coss), are also smaller than the silicon power MOSFET, so as to realize higher switching speed and smaller switching loss.

-

Commonly there are two methods to detect the drain current. First, we can cascade a very small resistance R on the GaN HEMT, and the voltage of the resistance is VR (VR ?I? ·R). By detecting the voltage of the resistance, it can realize the judgment of the overcurrent fault. Second, we can detect the drain-source voltage of GaN HEMT V?? to realize the detection of its drain current I?.

-

Vds change more obvious compared with VR

X. Lyu, H. Li, Y. Abdullah, and K. Wang, “A Reliable Ultra-Fast Short Circuit Protection Method for E-mode GaN HEMT,”, IEEE Transactions on Power Electronics, vol. 8993, no. c, 2020.

-

The figure given below SC ruggedness of different type of transistors. E-HEMTs are able to survive longer than 10us under less than 350V.

-

Under the short circuit conditio, the monitored phase-leg voltage (Vplv) will show a sudden dip due to the parasitic inductance in the power loop and a high di/dt. When the sudden voltage dip is detected, the fault trigger flag will be set.

-

A conventional desaturation detection circuit is deployed to confirm the short circuit fault and slowly turns off the device.

-

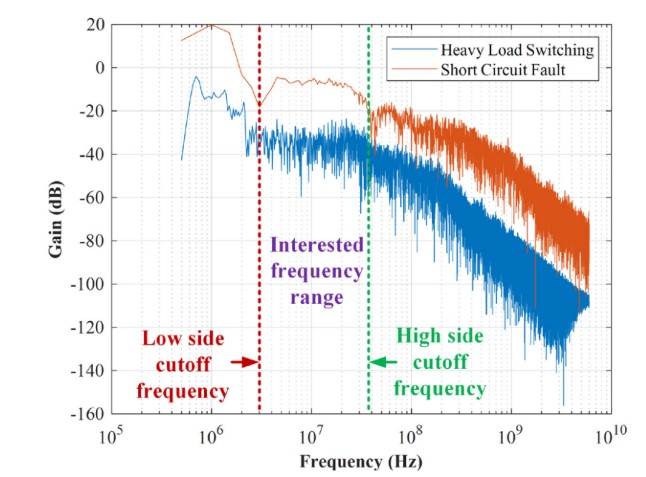

Generally, the amplitude of the phase-leg voltage under fault condition is higher than that under heavy load switching. Specifically, there is noticeable amplitude difference between these two voltages at the frequency band between 3 MHz and 50 MHz.

-

For the gate loop PCB layout, small gate loop is preferred to reduce gate voltage noise and prevent false turn-on during the switching transients. Also, there should be no trace overlap between the primary side and secondary side. For the high side switch gate drive, the CMTI of the power supply, isolator and isolated gate driver needs to be at least 100 V/ns. The barrier capacitance is preferred to be in few pico-farads.

K. Sun, J. Wang, R. Burgos, D. Boroyevich, Y. Kang, and E. Choi, “Analysis and design of an overcurrent protection scheme based on parasitic inductance of SiC MOSFET power module,” Conf. Proc. - IEEE Appl. Power Electron. Conf. Expo. - APEC, vol. 2018-March, pp. 2806–2812, 2018.

-

However, since these current sensing methods are not designed specifically for short circuit protection, they usually have problems of hard to integrate, not enough current range or not enough bandwidth for short circuit detection.

-

In addition, the I-V curve of SiC MOSFET is more temperature dependent compared to that of Si IGBT, which makes DeSat an unpractical method for SiC MOSFET short circuit protection under a wide temperature range.

-

The impedance of the Rs and Cs branch should be much larger than the parasitic inductor Lp branch so that this short circuit protection scheme will not affect the normal operation of the switch as shown in equation

J. Acuna, J. Walter, I. Kallfass, and G. N. Gan, “Very Fast Short Circuit Protection for Gallium-Nitride Power Transistors Based on Printed Circuit Board Integrated Current Sensor Keywords,” pp. 1–10.

-

(Desaturation) can be used without a special transistor package but requires a blanking time, which limits the speed of the short-circuit detection under Hard Switch Fault (HSF) type of faults, an issue which is critical for GaN transistors

-

This paper investigates the use of a PCB-integrated current sensor to perform a very fast short circuit detection especially dedicated to GaN power transistors. Two different short circuit detection methods were implemented using the integrated current sensor, neither of these methods uses a blanking time nor require a special transistor or special package.

R. Hou and J. Lu, “An ultrafast discrete protection circuit utilizing multi-functional dual-gate pads of GaN HEMTs,” 2019 IEEE Energy Convers. Congr. Expo. ECCE 2019, pp. 818–823, 2019.

-

In this paper, the discrete protection circuit is applied to the GaN HEMT by utilizing the GaNPX® dual-gate pads structure. By doing so, it can keep the conventional, straightforward gate driver loop layout of GaN and also provide the flexibility in terms of power loop layout. In other words, depending on the specific PCB system structure, system designers can choose to place the protection circuit either on the same side of the gate driver or the opposite side to the gate driver.

-

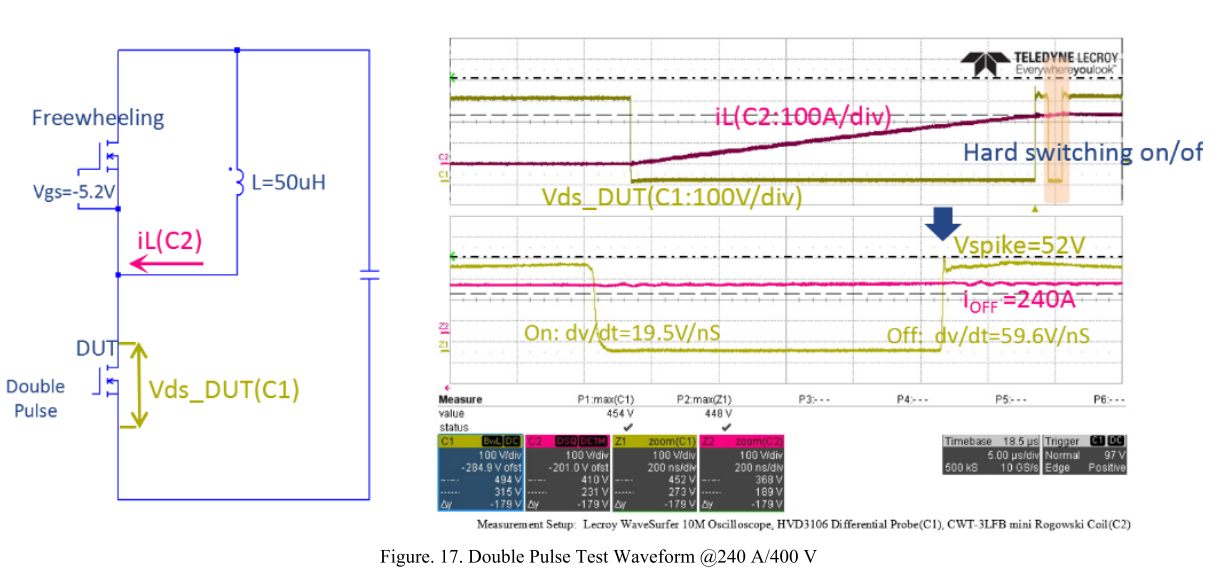

Fig. 4 shows the hard switch-on peak currents under 400 V with different load currents. If the load current is around 4 A, the peak current on the device can be 7 times higher to the load current. Therefore, it is important to guarantee the protection circuit will not be mis-triggered during this normal peak current transient

-

Therefore, the diode is preferred to have relatively small reverse recovery. In addition, during this transition, the parasitic capacitance of the diode also needs to be charged. Thus, to reduce the capacitance value, it is also desired to have two of these diodes in series.

K. Wang et al., “A Reliable Short-Circuit Protection Method with Ultra-Fast Detection for GaN based Gate Injection Transistors,” in 2019 IEEE 7th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2019, vol. 0, pp. 43–46.

-

This paper presents a new short-circuit protection method developed for Gallium Nitride (GaN) gate injection transistors (GITs).

-

Reducing the gate current during a short circuit fault helps to lower the short circuit energy, extend the short circuit survive device time, and prevent degradation.

-

The de-saturation detection has been widely used for protection against short circuit events for its reliability. Due to the relatively long blanking time, its total protection time is usually within a range of microseconds.

-

The proposed three-step short-circuit protection method is based on an ultra-fast fault detection, followed by the active gate current clamping, and the de-saturation protection confirmation. The proposed detection method utilizes the effect of the short circuit event’s high di/dt on the stray inductance in the power loop.

-

Compared to a normal operation condition, the di/dt during short-circuit faults is usually larger. Thus, the amplitude of the resulting voltage dip under the short-circuit conditions can be differentiated from normal conditions. The voltage dip occurs as soon as the short-circuit fault occurs, and then the voltage is gradually damped as the decoupling capacitor provides the energy for the short circuit current.

R. Hou, J. Lu, and D. Chen, “An Ultrafast Discrete Short-Circuit Protection Circuit for GaN HEMTs,” 2018 IEEE Energy Convers. Congr. Expo. ECCE 2018, pp. 1920–1925, 2018.

-

The traditional SCP/OCP methods can be summarized as below, 1) integrated de-saturation detection in gate-driver; 2) current sense resistor; 3) di/dt detection by voltage sensing across common source inductance [10]-[12]. However, the delay time for the traditional integrated de-saturation detection in gate-driver is typically about 2.5 μs, which might be slow for GaN HEMT; The current sense resistor will add additional parasitic inductance into the power circuit, which will affect the switching performance; The voltage sensing across common source inductance is not practical for GaN, as the stray inductance in the circuit must be minimized.

-

Clearly, with higher junction temperature, the saturation current gets lower. The second factor that contributes to the saturation current reduction can be on the gate. It has been proven that the fast increase of the temperature has an effect on the gate current [9]. With a higher temperature, the gate current becomes higher. Therefore, it introduces a larger voltage drop on the gate. This can be another reason cause the saturation current reduction.

Lu, J. L., & Chen, D. (2017). Paralleling GaN E-HEMTs in 10kW-100kW systems. Conference Proceedings - IEEE Applied Power Electronics Conference and Exposition - APEC, 3049–3056. https://doi.org/10.1109/APEC.2017.7931131

-

The main challenge for parallel operation is thought to be the diverse parasitics of the power stage and gate driver circuits, which are very sensitive to the high di/dt and dv/dt.

-

As Vgs increase, d(Id)/dt will start to affect Vgs via mutual loop and power commutation loop as described in many previous works. To minimize this effect, the Kelvin terminal is usually employed in high-frequency applications to bypass the common source inductance.

-

However, though the paralleled transistors will share the same gate driver chip and employ Kelvin connections in the design, d(Id)/dt could still potentially be problematic due to the existence of the quasi-common-source inductance. The imbalanced quasi-common source inductance or di/dt will eventually cause a resultant feedback voltage across the Vgs.

-

On one hand, the unbalanced quasi-common will help balance dynamic current distribution by lowering the transistor Vgs of higher transition speed. On the other hand, the feedback voltage might potentially cause overshoot or undamped ringing on Vgs.

-

For layout design, it is suggested to minimize and evenly distribute the quasi-common source inductance, which is so critical that an unsynchronized gate driver circuit is proposed to solve unbalanced quasi-common source inductance issue.

-

According to the law of electromagnetic induction, with the multi-layer magnetic-flux-canceling design strategy, the parasitics of the trace could be greatly reduced – the direction of the commutation current on two adjacent layers are opposite so that the generated flux outside the loop are canceling each other.

-

Generally speaking, in hard switching application, the more transistors we parallel, the higher switching loss we will have.

-

Parasitic capacitance of PCB and magnetic components is not ignorable compared with the ultra-small Coss of GaN HEMT. The parasitic capacitance in a half bridge module is extracted by ANSYS Q3D as Figure 13, indicating the parasitic capacitance in one leg is 0.6 nF (0.4 nF to BUS+ and 0.2 nF to BUS- node).

Mao, H., Abdel Rahman, O., & Batarseh, I. (2008). Zero-voltage-switching DC-DC converters with synchronous rectifiers. IEEE Transactions on Power Electronics, 23(1), 369–378. https://doi.org/10.1109/TPEL.2007.911768

-

In low-output-voltage dc–dc converters, SRs are widely utilized to reduce rectifier conduction loss and improve converter efficiency. However, during switches’ transition, SRs’ parasitic body diodes unavoidably carry load current, which decreases conversion efficiency because voltage drop across body diodes is much higher than that across SRs.

-

The reverse recovery problem of MOSFET body diodes is a barrier to SRs’ applications with higher voltage, for example, SRs with 200 V and higher voltage ratings are hardly found in applications, because SR body diodes’ reverse recovery is more severe with increased voltage ratings, which significantly increase switches’ and body diodes’ switching loss.

-

Recently, soft-switching techniques draw a lot of attention in reducing switching loss and electromagnetic interference (EMI) noises.

-

Quasi-resonant converters (QRCs) were introduced to overcome the disadvantages of conventional pulse width modulation (PWM) converters operating at high switching frequency by achieving ZVS for the active switch and zero current switching (ZCS) for the rectifier diode

-

By reducing the filter inductance in the conventional PWM converters, ZVS quasi-square-wave (QSW) technique offers ZVS for both the active and passive switches without increasing the switches’ voltage stress [3], [4], [13]. However, QSW converters suffer high current stress in components, as a result, conduction losses are greatly increased, and active switches turn off at high currents.

-

Due to the SR’s body-diode reverse-recovery current, the active switch suffers from extra turn-on loss, and the SR’s body diode suffers from hard turn-off loss. In short, in the SR buck converter, active switch operates at undesirable conditions of hard turn-on; the SR operates at ZVS turn-on, but the body diode’s reverse recovery leads to extra switching loss and EMI problems.

-

The ideal switching operation is: all switches’ body diodes conducts prior to turn-on of the switches, and all switches turn off with inductive load instead of capacitive load. In other words, to avoid body diode’s hard turn-off, the current commutation sequence must be from a switch to a body diode instead of from a body diode to a switch.

P. Das, S. A. Mousavi, and G. Moschopoulos, “Analysis and design of a nonisolated bidirectional ZVS-PWM DC-DC converter with coupled inductors,” IEEE Trans. Power Electron., vol. 25, no. 10, pp. 2630–2641, 2010.

-

The batteries are connected to the buses with bidirectional dc–dc converters that allow them to discharge or to be charged when necessary.

-

The nonisolated converters are less expensive than the isolated ones, as they need fewer active switches and passive components.

-

The coupled inductors allow the converter to have a steep voltage conversion ratio that keeps the duty cycle from becoming too narrow (when the converter is in the buck mode of operation), or too wide (when the converter is in the boost mode of operation).

-

The earlier proposed ZVS techniques for non-isolated bidirectional dc–dc converters can be categorized as follows.

-

Buck/boost converters that are made to operate with an inductor (Lin ) current that flows in both directions during each switching cycle. The inductor current, however, has a high ripple and must flow in both directions. This results in high turn OFF and circulating current losses.

-

Quasi- or multiresonant converters that have high-switch peak voltage stresses and are difficult to control and implement.

-

Zero-voltage transition (ZVT) converters that use auxiliary circuits to help the switches operate with ZVS.

J. W. Yang and H. L. Do, “High-efficiency bidirectional dc-dc converter with low circulating current and ZVS characteristic throughout a full range of loads,” IEEE Trans. Ind. Electron., vol. 61, no. 7, pp. 3248–3256, 2014.

- The big advantage of an isolated bidirec- tional dc–dc converter is galvanic isolation which is an effective method for breaking a ground loop. However, this converter requires an isolated transformer and more than four switches for galvanic isolation so that its efficiency is lower than that of a nonisolated-type converter [8]–[13]. On the other hand, the advantages of a nonisolated bidirectional dc–dc converter are simple structure, fundamentally including an inductor and two switches, and higher efficiency than an isolated-type converter.

M. Pavlovsky, G. Guidi, and A. Kawamura, “Buck/boost DC-DC converter topology with soft switching in the whole operating region,” IEEE Trans. Power Electron., vol. 29, no. 2, pp. 851–862, 2014.

-

One of the main motivations behind the proposed topology was also to keep it as simple as possible. The simplicity was especially important from the ease of structural layout point of view.

-

The topology was implemented in a 14 kW converter prototype operating at 62.5 kHz and tested with complete closed-loop control. Experimental efficiencies in the range of 98.5% show that the proposed circuit is highly capable while remaining sufficiently simple.

W. Lee, D. Han, C. Morris, and B. Sarlioglu, “Minimizing switching losses in high switching frequency GaN-based synchronous buck converter with zero-voltage resonant-transition switching,” 9th Int. Conf. Power Electron. - ECCE Asia "Green World with Power Electron. ICPE 2015-ECCE Asia, pp. 233–239, 2015.

-

In this paper, a GaN-based synchronous buck converter operating with zero-voltage resonant-transition (ZVRT) switching in synchronous conduction mode is proposed. The ZVRT switching converter offers a favorable trade-off between switching and conduction losses especially in GaN-based DC-DC converters.

-

However, GaN devices are more suitable for 600 V or less voltage level and lower power applications than SiC due to its high electron mobility and size advantage.

-

The basic concept and the experimental results of a zero-voltage-switched quasi-resonant-wave (ZVS-QSW) converter, which is also called zero-voltage resonant-transition (ZVRT) switching converter, operating at 1 MHz is presented in reference.

-

This soft switching can be obtained by choosing an appropriately valued inductor such that the peak-to-peak inductor current (current ripple) is always higher than twice the average output current. This technique is relatively simple to achieve since it does not require either additional passive and active components or a complicated control loop. However, the main disadvantage of this converter is the high conduction losses due to the two times higher current ripple. Because of the high conduction losses, this technique is not suitable for applications where minority carrier devices, such as IGBTs.

-

With GaN-based ZVRT switching converters, the low switching losses can be achieved while not significantly increasing their conduction losses. Furthermore, a current spike due to the high dv/dt of the GaN device and the output capacitance, Coss can be decreased with soft switching and it also helps to minimize the switching losses.

-

To achieve soft switching with the ZVRT switching converter, an appropriately sized inductor value is the most important design consideration. The inductor value needs to be the maximum inductance that enables the ZVRT switching while keeping the inductor current ripple as small as possible.

-

The value K must be greater than 2 to have the negative current for soft switching. In general, it is set to be 4 to have three to one ratio of the turn-on and turn-off transitions for the switching devices.

- Especially the switching device loss of Q1 is decreased from 2.6 W to 0.16 W due to soft switching. The switching device loss of Q2 is increased due to the high reverse current flowing into the device at the switching transition. In addition, the capacitor conduction loss due to the equivalent series resistance (ESR) increases in ZVRT converter because of the high current ripple. The overall converter losses are decreased by 50% at maximum in ZVRT converter compared to the conventional converter.

X. Huang, F. C. Lee, Q. Li, and W. Du, “High-Frequency High-Efficiency GaN-Based Interleaved CRM Bidirectional Buck/Boost Converter with Inverse Coupled Inductor,” IEEE Trans. Power Electron., vol. 31, no. 6, pp. 4343–4352, 2016.

-

The resonant period in CRM is less with an inverse coupled inductor than with a noncoupled inductor, which is beneficial for the high-frequency operation.

-

THE bidirectional buck/boost converter is widely used in the power electronics system due to its simplicity and high efficiency, such as the on board charger/discharger for plug-in hybrid electric vehicles [1]–[3], and the interfaced converter for the energy storage systems [4], [5].

-

Critical current mode (CRM) operation is the most simple and effective way to achieve ZVS, and is widely used in medium-low power applications [8], [11], [13]. CRM operation introduces a large current ripple, which is at least twice of the load current. It is necessary to interleave multiple phases to cancel the switching frequency current ripple and lead to a smaller EMI filter.

-

Furthermore, the resonant period formed by the inductor and device junction capacitors is too long at high frequency, which leads to a large circulating energy.

-

Switch Ts is the main switch in the buck direction, while Bs is the main switch in the boost direction. If the main switch turn-on instant is set to exactly half the resonant period after the inductor current crosses zero via any zero-current detection technique, the switch achieves minimum voltage turn-on.

-

Another limiting factor of CRM operation at high frequency is the resonant time Tr , which is half of the resonant period formed by L and the junction capacitors of the devices.

-

One way to solve the limitations of conventional CRM operation is to utilize the quasi-square-wave soft-switching technique. However, the negative portion of the inductor current grows larger under light-load conditions, which will significantly deteriorate the converter efficiency. Another solution is to use a coupled inductor to improve the CRM performance, including ZVS range extension/circulating energy reduction and resonant period reduction.

-

This paper aims to analyze the benefits of the inverse coupled inductors in CRM operation based on a 1-MHz interleaved buck/boost converter with GaN devices.

-

380V to 150V @ 1MHz, 98.5%, 8A at output max.

T. Konjedic, L. Korošec, M. Truntič, C. Restrepo, M. Rodič, and M. Milanovič, “DCM-based zero-voltage switching control of a bidirectional DC-DC converter with variable switching frequency,” IEEE Trans. Power Electron., vol. 31, no. 4, pp. 3273–3288, 2016.

-

A major concern in synchronous dc–dc converters is the reverse recovery effect of the synchronous transistor’s antiparallel body diode at the instant of turning ON the main transistor (mainFET). For the duration of the reverse recovery phenomena, both transistors are exposed to high current change rates and high peak reverse recovery currents, which significantly increase switching losses, cause electromagnetic interference, and lead to dangerous operating conditions. Another drawback of hard-switched converters that utilize synchronous rectification is the unwanted Cdv/dt-induced turn-on of the synchronous transis- tor (syncFET) immediately after its body diode recovers.

-

The ever more demanding requirements for compact, lightweight, and small-sized power converters are pushing their operating frequencies to the values where the sizes of the pas- sive components in the circuit can be significantly reduced. The main negative effect of operating at such high switching frequencies is the increase in switching losses and the resulting lower power conversion efficiency. In order to overcome this drawback, zero-voltage switching (ZVS) approaches are widely applied to all kinds of switching power converters. The utilization of ZVS alleviates the switching losses and significantly decreases the rate of power conversion efficiency deterioration with increasing switching frequency. As a consequence, much higher power densities can be achieved at unaffected power conversion efficiencies.

-

The key for achieving zero-voltage turn-on of the syncFET in both CCM and DCM is in providing a sufficiently long dead time, i.e., time interval between turning OFF the mainFET and turning ON the syncFET.

-

In order to achieve zero-voltage turn-on of the mainFET, the turn-off instant of the syncFET has to be delayed to the point at which the inductor current iL reaches a certain value in the direction that opposes the primary energy flow in a synchronous converter. This value is designated as the reversed current IR. The selection of its value is of crucial importance since an insufficient IR cannot provide enough charge to completely discharge CossH and charge CossL to the voltage.

-

This paper has proposed a digital control scheme for achieving ZVS throughout the entire operating range of a conventional bidirectional dc–dc converter.

G. Chen, L. Chen, Y. Tao, Y. Deng, and X. He, “Zero-voltage-switching synchronous buck converter with coupled inductor,” Diangong Jishu Xuebao/Transactions China Electrotech. Soc., vol. 31, no. 8, pp. 102–110, 2016.

-

However, at the moment that the upper switch turns on, it provokes the reverse recovery phenomenon of the antiparallel body diode of the synchronous switch [3]–[7]. During this interval, the switches are submitted to a high current change rate and a high peak of reverse recovery current, as shown in Fig. 1(b). These two effects significantly contribute to increase switching losses and electromagnetic interference, which may offset the benefits of using the synchronous switch.

-

The ZVS control scheme can reduce the switching loss. However, DCM/CCM boundary operation increases the ripple component of the inductor current. The large conduction loss due to high ripple components lowers the overall efficiency. In order to minimize the conduction loss and the output voltage ripple, the CCM operation needs to be maintained.

Q. Huang and A. Q. Huang, “Variable Frequency Average Current Mode Control for ZVS Symmetrical Dual-Buck H-Bridge All-GaN Inverter,” IEEE J. Emerg. Sel. Top. Power Electron., vol. PP, no. c, pp. 1–1, 2019.

-

From 2014 to 2016, Google and IEEE hosted a world-wide competition, Little Box Challenge, aiming to achieve the highest power density for a 2kW single-phase PV inverter. Several teams of the 18 finalists, such as the ETH team, the Fraunhofer team and the winning team Red Electric Devils, proposed a similar inverter topology which was the symmetrical dual-Buck H-bridge (DBHB) inverter topology [12]-[14]. The winning team Red Electric Devils achieved power density of 142.9W/in3(8.7kW/l) [14]. Due to this competition, the DBHB inverter topology, shown in Fig. 1, has drawn great attention in industry and academia [12]-[15].

-

The ZVS technique can help the symmetrical DBHB GaN inverters push the switching frequencies much higher compared to the hard- switching technique. ZVS symmetrical DBHB GaN inverters are drawing more interests than the hard-switching ones, since the ZVS GaN inverters have more potential of high power density than the hard-switching GaN inverters.

-

ZVS is realized by pushing the lower current reference band to the required negative valley current.