This repository contains scripts, reference designs, and tutorials for the Intel FPGA Partial Reconfiguration design flow.

- Tutorials are located in the tutorials sub directory

- Reference Designs are located in the ref_designs sub directory

- Software and Linux drivers are located in the software sub directory

- Scripts are located in the scripts sub directory

- Verification components for simulation are located in the verification sub directory

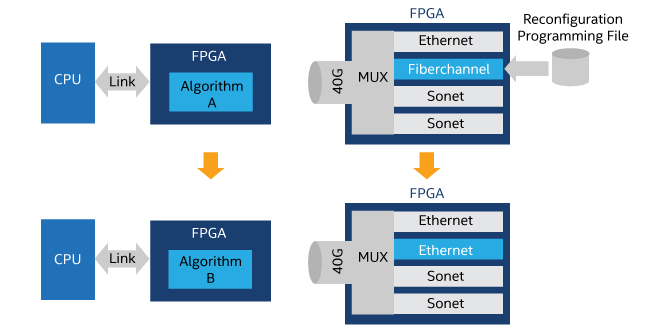

The Partial Reconfiguration Design Flow is supported in the Intel Quartus Prime® Pro Edition software for Intel Arria 10 Devices with the following key features:

- Command line and graphical user interface for compilation and analysis

- Hierarchical Partial Reconfiguration that allows you to create child PR partitions in your design

- Simulation of Partial Reconfiguration that allows you to observe the resulting change and the intermediate effect in a reconfiguration partition

- Signal Tap debug with simultaneous acquisition of both the Static region and Partial Reconfiguration regions

- Refer to the Intel® Quartus® Prime Pro Edition User Guide: Partial Reconfiguration for information about Partial Reconfiguration

Releases are created for each major version of Quartus Prime Software. It is recommended to use the release for your version of Quartus Prime.

More information available at http://www.01.org/fpga-partial-reconfig